# ESP2

# **ENSONIQ SIGNAL PROCESSOR 2**

#### Part I

**Instruction and Hardware Specification**

1995

David Andreas Jon Dattorro J. William Mauchly

| 0. Introduction |                |                                                       |    |  |

|-----------------|----------------|-------------------------------------------------------|----|--|

| 1.              | Chip Overvie   | N                                                     | 6  |  |

|                 |                | Architecture                                          |    |  |

|                 | 1.             | 1.1. Function Units: MAC, ALU, AGEN                   | 8  |  |

|                 |                | 1.2. Internal Registers.                              |    |  |

|                 |                | able 1. Internal Register Address Map                 |    |  |

|                 |                | 1.3. GPR and AOR                                      |    |  |

|                 | 1.             | 1.4. SPR                                              | 9  |  |

|                 | 1.             | 1.5. Internal Register Usage                          | 10 |  |

|                 | T              | able 2. Registers as Operands                         | 10 |  |

|                 | 1.             | 1.6. Instruction Memory                               | 10 |  |

|                 | 1.             | 1.7. Future Expandability                             | 10 |  |

|                 | 1.             | 1.8. Internal Operand Busses                          | 10 |  |

|                 |                | 1.9. External Interfaces                              |    |  |

|                 |                | ruction Cycle Timing                                  |    |  |

|                 | 1.3. Late      | ncy                                                   | 13 |  |

|                 | 1.             | 3.1. Inter-Unit Latency                               | 13 |  |

|                 | 1.             | 3.2. Latency of External Memory Access via AGEN       | 13 |  |

| 2.              | Multiplier/Ac  | cumulator/Shifter                                     | 15 |  |

|                 | 2.1. Arch      | nitecture                                             | 15 |  |

|                 | 2.             | 1.1. Exception Processing                             | 17 |  |

|                 | T              | able 3. Multiplier Exceptions                         | 17 |  |

|                 | 2.2. MAG       | C unit Barrel Shifter                                 | 17 |  |

|                 | 2.3. Acce      | ssing the MAC unit                                    | 17 |  |

|                 | 2.             | 3.1. Writing the MACP (Preload) latch                 | 18 |  |

|                 | 2.             | 3.2. Reading the MAC latch                            | 18 |  |

|                 | 2.             | 3.3. MAC Result Low latch (MACRL)                     | 18 |  |

|                 | 2.4. MAG       | C unit Instructions                                   | 19 |  |

|                 | T              | able 4. MAC unit List of Instructions                 | 19 |  |

|                 | 2.5. MAG       | C unit Pseudo Instructions                            | 20 |  |

| 3.              | ALU and Inst   | ruction Set                                           | 24 |  |

|                 | 3.1. ALU       | Instructions                                          | 25 |  |

|                 | 3.2. ALU       | Pseudo Instructions                                   | 42 |  |

|                 | 3.3. Con       | dition Code Register                                  | 48 |  |

|                 | 3.             | 3.1. Setting Condition Codes                          | 49 |  |

|                 | T              | able 5. CCR Setting by Instruction                    | 49 |  |

|                 | 3.             | 3.2. Conditional Execution Mechanism                  | 51 |  |

|                 | 3.             | 3.3. Instructions Not Skippable                       | 52 |  |

|                 | 3.             | 3.4. Arithmetic Condition Masking                     | 52 |  |

|                 |                | able 6. Arithmetic Condition Code Masks               |    |  |

|                 | 3.4. Inst      | ruction Cycle Execution Latency (Latent Instructions) | 54 |  |

| 4.              | Indirect Regis | ster Addressing                                       | 58 |  |

|                 | 4.1. Exce      | eptions to Indirection                                | 59 |  |

|                 | T              | able 7. Indirection Operand Availability              | 59 |  |

|                 | 4.2. Poin      | ter Register Latencies                                | 60 |  |

| 5.              |                | ory Refresh                                           |    |  |

|                 |                | ruction Refresh                                       |    |  |

|                 |                | and AOR Refresh                                       |    |  |

|                 | 5.             | 2.1. Internal Register Refresh during Suspension/Halt | 62 |  |

|                 |                | 2.2. Internal Register Refresh Collision              |    |  |

| 6.              | SPR Hazards    |                                                       | 63 |  |

| 7.  | External Data-Memory Interface                                      | 64 |

|-----|---------------------------------------------------------------------|----|

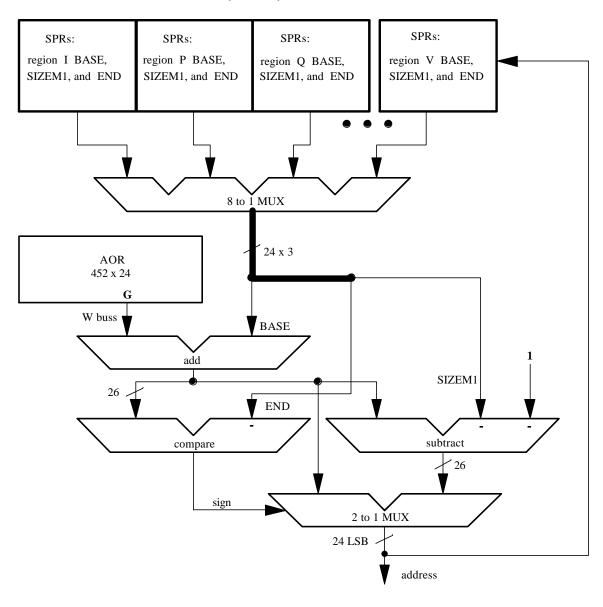

|     | 7.1. Address Generator (AGEN) Architecture                          |    |

|     | 7.1.1. AGEN Address Calculation                                     | 65 |

|     | 7.1.2. Plus-One Addressing Mode                                     |    |

|     | 7.1.3. Extent of the Modulo                                         | 66 |

|     | 7.1.4. Other External Memory Configurations                         | 66 |

|     | 7.1.5. UPDATE region BASE                                           |    |

|     | 7.2. AGEN Instructions                                              |    |

|     | 7.3. Accessing the Region Control Registers and AORs                | 67 |

|     | 7.4. External Memory Access                                         |    |

|     | 7.4.1. External Address Buss                                        |    |

|     | Table 8. External Address Pin Connection                            | 69 |

|     | 7.4.2. External Memory Data-Interface                               | 70 |

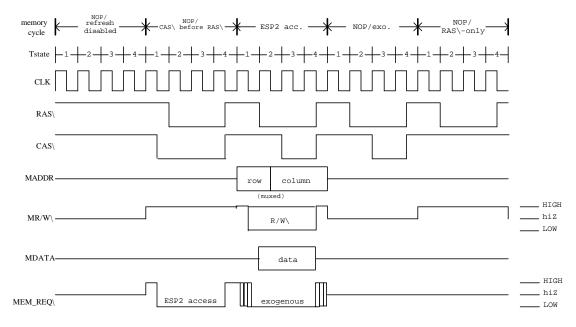

|     | 7.5. External DRAM Refresh                                          | 71 |

|     | 7.6. Initializing or Accessing External Memory from the System Host | 72 |

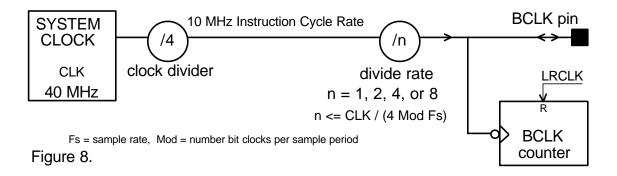

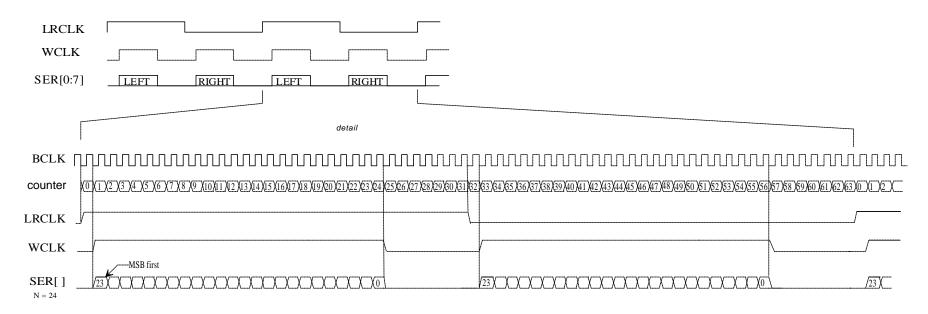

| 8.  | Serial Interface                                                    |    |

|     | 8.1. Serial Interface Control Registers                             | 73 |

|     | Table 9. Serial Interface Control Registers                         |    |

|     | 8.2. LRCLK                                                          |    |

|     | 8.3. WCLK                                                           | 74 |

|     | 8.4. BCLK                                                           |    |

|     | 8.5. An Example of Serial Interface Control Register Settings       | 75 |

|     | 8.6. Serial Interface Rules                                         |    |

|     | 8.7. Serial Reset and Synchronization                               |    |

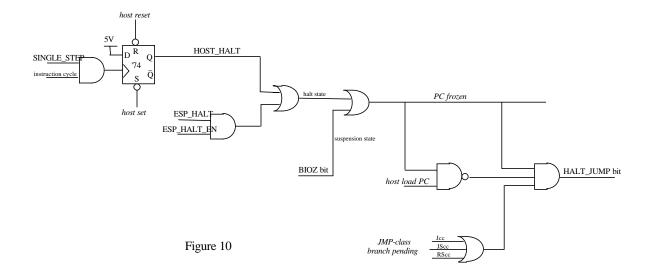

| 9.  | Halt and Suspension States                                          |    |

|     | 9.1. Halting the Chip                                               |    |

|     | 9.2. Chip State during Halt and Suspension                          |    |

|     | 9.3. Single Step Mode                                               |    |

|     | 9.4. Single Pass Operation                                          |    |

| 10. | Chip Reset, Initialization, and Synchronization                     |    |

|     | 10.1. Reset                                                         |    |

|     | 10.2. Initialization                                                |    |

|     | 10.3. Synchronization.                                              |    |

|     | Table 10. SYNC_MODE bit functionality                               |    |

| 11. | Special Purpose Registers                                           |    |

|     | 11.1 SPR Descriptions                                               |    |

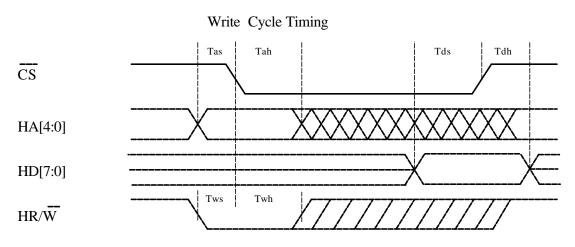

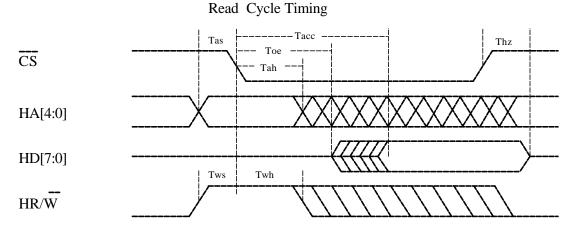

|     | Host/ESP2 Interface                                                 |    |

|     | 12.1. Host/ESP2-Register Interface                                  |    |

|     | 12.1.1. Writing GPR/AOR/SPR                                         |    |

|     | 12.1.2. Reading GPR/AOR/SPR                                         |    |

|     | 12.2. Host/ESP2-Instruction Interface                               |    |

|     | 12.2.1. Writing Instruction Memory                                  |    |

|     | 12.2.2. Reading Instruction Memory                                  |    |

|     | 12.3. Host Interface Registers                                      |    |

|     | 12.3.1. Testing                                                     |    |

|     | 12.3.2. Some Host Interface Register Descriptions                   |    |

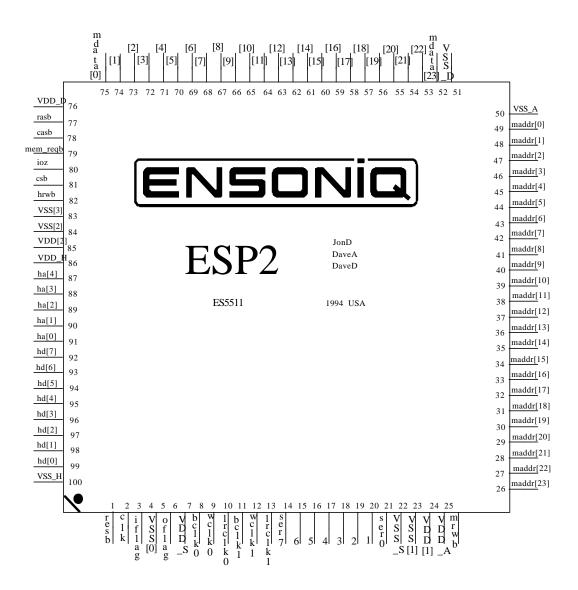

| 13  | Pin List.                                                           |    |

|     | Table 11. ESP2 Chip Pinout                                          |    |

|     |                                                                     |    |

# MISSING INFORMATION:

Serial, external memory, and host interfaces; setup & hold times. Recommend pull-up resistor values.

#### 0. Introduction

The demands of digital audio require particular features from DSP (Digital Signal Processing) chips for sound-effect design. The semiconductor industry serves a broader customer base, however. While several commercial processor chips are more or less suitable to the audio technical community, this is not what drives digital audio-based companies into the intense and expensive design cycle of custom VLSI. The principal driving force is the competitive edge gained by proprietary hardware which stifles reverse engineering. The primary end-product, of course, is software; the algorithms which drive the chips.

To remain competitive with contemporary products, a typical commercial sound-effects box needs to execute roughly 30 different algorithm types, each satisfying certain artistic standards of quality. While in the throes of an audio signal processor design, a DSP guru from CCRMA, Stanford University, theorized that most DSP algorithms can be formulated in terms of the digital filter. [Moorer] Reverberation algorithm design, however, remains more of an artistic endeavor than a science; this elusive specialty is still dominated by a few companies having the benefit of an early start. [Blesser/Bader] [Griesinger]

Having this mandate, three design engineers were given carte blanche in 1990 to improve upon an existing and proven chip design known as ESP. Rarely does an audio-product specification call for the algorithm designers to engineer the computer as well. The outcome is the fixed-point ESP2 which, as it turns out, exceeds the capabilities of commercial DSP chips with regard to audio processing efficiency.

The purpose of Part I, the *Hardware (or Chip) Specification*, is to explain the ESP2 chip design philosophy as it pertains to DSP applied to audio. The ESP2 programming Language is discussed in Part II, often referred to as the *Software Specification*. We discuss effect design and present algorithms for several practical and real Audio Applications in Part III. We do this, first, to highlight the efficiency of the ESP2, second, as an exposition of how fundamental DSP operations are accomplished in real-time, third, to present some new results in the field of audio and DSP.

# 1. Chip Overview

Part I fully explains the functionality of the Digital Signal Processor chip called ESP2. To assist the programmer, this *Chip Spec.* explains the implementation of all the ESP2 instructions. The information required by the engineer to design this chip into some system is also found here, and is explained so as to be accessible to programmers having a limited hardware background.

The information regarding the instructions is supplemented in Part II, the Language and Software Spec., which explains nuances of the syntax which is the ESP2 assembly language. The ESP2 language resembles some aspects of the C programming language. The language is easy to learn, intuitive, and truly a step up from the standard practice of manipulating unmeaningful register names.

The Software Spec. should be read by anyone using the ESP2 for intensive operations involving external memory access (e.g., Reverberator design). Other engineers wishing to write simpler test programs can get by with Part I and an example of a complete ESP2 program from which they may derive a shell to work within. Programming examples can be found in the Applications section, Part III. The References are found thereafter.

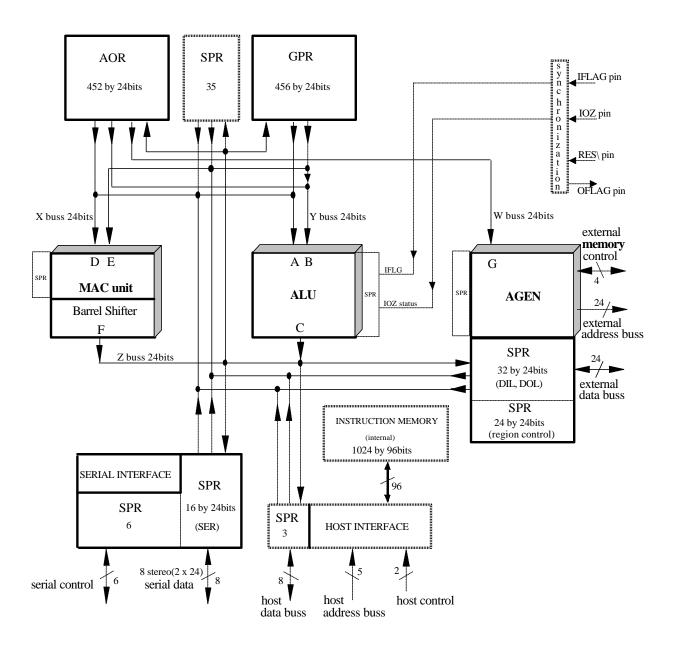

The ESP2 chip architecture, shown in Figure 1, is optimized for the processing of audio signals. The demands of audio dictate a minimum single precision bit-width of 24 bits. The most prominent feature of this architecture is the three parallel function units: Address Generator (**AGEN**), Arithmetic Logic unit (**ALU**), and Multiplier/Accumulator/shifter unit (**MAC unit**).

Each function unit is complemented by extra source/destination registers called **SPR** (Special Purpose Register). These registers all have unique purposes specialized to the unit that they support. In many instances SPRs increase the number of operands employed by a single instruction.

The AGEN is supported by a distinct block of registers called **AOR** (Address Offset Register), which facilitate random access of off-chip data on each instruction cycle. These registers provide address offsets to AGEN's modulo address calculation mechanisms. Unlike conventional DSP chips, the AORs facilitate the design of sparse digital networks which is a requirement of audio signal processing; e.g., digital reverberators.

Both the ALU and the MAC unit perform their three-operand instructions <u>directly</u> on all the internal registers including **GPR** (General Purpose Register). MAC unit and ALU direct access of SPR is useful to control the many specialized processes. The AORs are directly accessible from the ALU and MAC unit for the purpose of modulating addresses or for any general purpose. This feature is useful for time-varying processes.

The instruction memory is 96 bits in width and completely internal; i.e., there is no provision for off-chip program memory. This large instruction word supports the parallel architecture such that all three units can function in parallel while the instruction set supports this. While the ESP2 also supports standard program control operations such as branching and calls to subroutines, there are hardware provisions for program space conservation. This conservation includes a low-overhead looping mechanism and conditionally executable instructions. The latter feature eliminates the overhead associated with branching around status dependent code, and improves efficiency three-

fold through the selective conditional execution of any or all of the parallel function unit operations.

Although the ESP2 is inherently a parallel/pipeline design, all ESP2 instructions individually execute in the same amount of time (one instruction cycle, four system clocks) under all circumstances.

# 1.1. Chip Architecture

Figure 1. ESP2 Chip Architecture

# 1.1.1. Function Units: MAC, ALU, AGEN

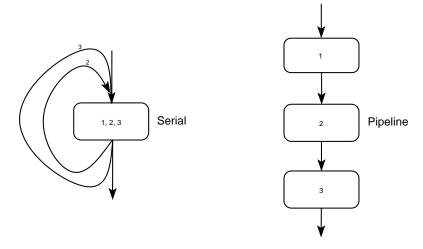

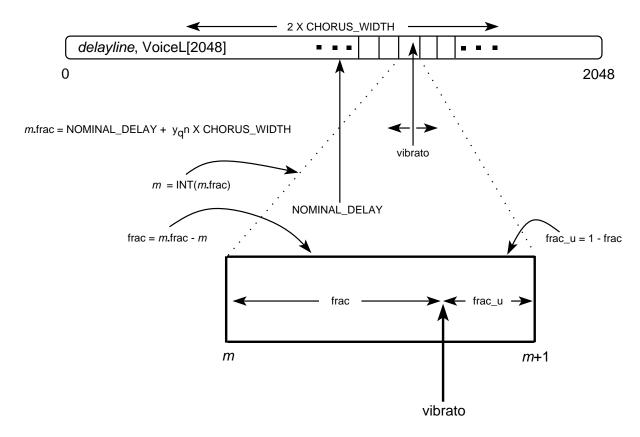

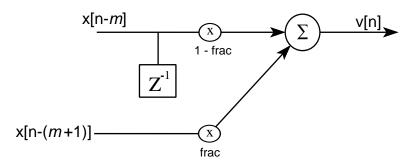

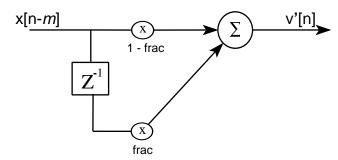

The three main function units are designed to execute in parallel employing an instruction set which supports the parallelism. The internal *pipeline* design dictates a specific hardware ordering-in-time which sees the MAC unit first, followed mid-cycle by the ALU. The AGEN timing exactly parallels that of the MAC unit. Some of the inter-unit pipeline latencies discussed (see the Instruction Cycle Timing diagram), will be more easily understood if this ordering-in-time is kept in mind.

The order of each instruction *field*, on the programmer's single line of code (one **instruction cycle**, one program line, one instruction line), within which each unit's instruction will be found is:

MAC unit ALU AGEN

The latencies are few, while easy-to-understand charts are presented in the Software Specification to assist the programmer. It is important that the programmer recognize that the speed and efficiency of the ESP2 processor for most all DSP tasks is facilitated by this pipeline design.

One benefit of the parallelism is that the programmer will find many common instructions amoung the units; e.g., both the MAC unit and ALU have identical MOV and identical shift (ASH) syntax, so the programmer can simply cut and paste into the appropriate field.

The MAC unit is a three operand device (two source, one destination), plus a seed source. The MAC unit instruction set comprises 20 fundamental instructions, 10 variations, and an assortment of pseudo instructions providing a large palette of multiply/accumulate/shift operations. A prominent feature of the MAC unit is the ability to selectively inhibit latching of the accumulator result while sending it to some destination register. A Barrel Shifter is integral to the MAC unit, available on a perinstruction basis, and can be accessed by the ALU. The Barrel Shifter can be used to shift either the input to the accumulator or the accumulator output.

The ALU instruction set consists of 32 standard, non-standard, and Boolean instructions. All of these instructions can take two source operands and another destination operand. The non-standard operations are used for such things as FFTs, envelope generators, stereo-to-mono signal conversion, etc. The ALU instruction set is augmented with a wide assortment of pseudo instructions. Program control instructions which allow conditional branching are found in the ALU. While branching allows the programmer to jump over parallel instructions to the ALU, MAC unit, and AGEN, a separate mechanism allows conditional execution of individual instructions to any or all of the three function units.

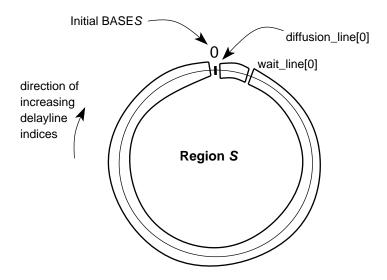

The AGEN performs modulo addressing of 8 distinct regions of data located nearly anywhere in external physical memory and of any size. Within each region can be defined numerous delaylines whose region address offsets are determined by the multiplicity of AORs employed by AGEN. AGEN features include a Plus-One addressing mode, and UPDATE of the region BASE under program control. The AGEN can also perform absolute addressing as would be required for peripheral I/O.

#### 1.1.2. Internal Registers.

Operand addresses are 10 bits allowing up to a total of 1024 internal registers. This register space is apportioned as follows:

## Table 1. Internal Register Address Map

\$000 - \$1c7 General Purpose Registers (GPRs)

| \$1c8 - \$1ff | Special Purpose Registers (SPRs) |

|---------------|----------------------------------|

| \$200 - \$3c3 | Address Offset Register (AORs)   |

| \$3c4 - \$3ff | Special Purpose Register (SPRs)  |

The ESP2 instruction set operates directly on these registers given meaningful names by the programmer.

The MAC unit (with one restriction) and ALU can utilize all the registers as operands.

#### 1.1.3. GPR and AOR

GPRs (General Purpose Registers) and AORs (Address Offset Registers) are 24-bit wide registers implemented as large dynamic ram arrays. GPRs and AORs have two read ports and one write port. Each of the ports is accessed twice per instruction cycle. This gives a virtual set of four read ports and two write ports per instruction cycle for each of the arrays.

The GPR read ports allow two operand fetches for the ALU and two for the MAC unit in an instruction cycle. The two GPR write ports allow one result-write by the ALU and one by the MAC unit.

The AOR array is used to hold address offsets for the AGEN. When not used for holding address offsets, AORs may be used just like GPRs. The four AOR read ports allow one offset fetch for the AGEN, one operand fetch for the MAC unit, and two operand fetches for the ALU. The two write ports of the AOR allow one result-write by the ALU and one by the MAC unit.

Host access to GPR and AOR is governed by the ALU.

Because these registers are dynamic RAM they must be refreshed to maintain the data. The mechanism for refreshing these registers is somewhat transparent and built into the instruction set. GPR and AOR power-up in their lower power state; i.e., when these registers read as logical 1, they are in their lower power consumption state.

The address map allows 456 GPRs and 452 AORs. Due to die size limitations, it is not at first planned to include all of these registers. The initial revisions will have 256 GPRs and 256 AORs.

#### 1.1.4. SPR

SPRs (Special Purpose Registers) are static registers for holding data specific to a particular operation of a function unit, for interfacing to the external ports of the chip, for controlling certain operating modes, or for chip hardware configuration and status. Internal chip control and status registers, such as the Program Counter (PC) or the Condition Code Register (CCR), are mapped as SPRs to provide access via the system host. Host access to SPR is governed by the ALU.

All the function units (ALU, AGEN, MAC) have supporting SPRs. In some instances, one or several SPRs effectively behave as extra <code>source/destination</code> operands to a particular function unit. Unless stated otherwise, these extra source/destination SPRs are subject to the same inter-unit latencies as any conventional source/destination register. (See the section on Inter-Unit Latency.)

SPRs are accessible as operands in all of the same modes as GPRs, although some of the SPRs are read-only. SPRs are distributed over the GPR and AOR address space so as to balance the number of GPRs against the number of AORs.

#### 1.1.5. Internal Register Usage

The rules governing the use of the three types of registers as operands for the three function units are indicated in Table 2. (The symbol \* in Table 2 denotes a valid usage.) Notice that an AOR is not a valid E source operand in the MAC unit because one of the AOR's four virtual read ports is usurped by AGEN.

Table 2. Registers as Operands

|             | ALU |   |   | MAC unit |   |   | AGEN |

|-------------|-----|---|---|----------|---|---|------|

|             | A   | В | C | D        | E | F | G    |

| GPR         | *   | * | * | *        | * | * |      |

| AOR         | *   | * | * | *        |   | * | *    |

| SPR         | *   | * | * | *        | * | * |      |

| Buss        | X   | Y | Z | X        | Y | Z | W    |

| Source      | *   | * |   | *        | * |   | *    |

| Destination |     |   | * |          |   | * |      |

#### 1.1.6. Instruction Memory

The instruction memory is presently a 300 by 96-bit dynamic memory array. These 300 ESP2 instructions are equivalent to 900 instructions of a more conventional architecture because of the three parallel function units that constitute the ESP2. Future expansion sets the maximum possible number of ESP2 instructions at 1024 (3072 conventional). At a sample rate of 44.1 kHz and using a system clock of 40 MHz, ESP2 can execute 226 instruction cycles (678 conventional) per sample period.

The instruction memory cell has one write port and one read port and cycles at twice the instruction rate. This allows one cycle for instruction fetching, and a read/write cycle for refresh or host access to the instruction memory array. Refresh of instructions is transparent to the programmer. Instruction memory powers-up in its lower power state; i.e., when instruction memory reads as logical 1, it is in its lower power consumption state.

Instruction memory can be downloaded, overlaid, or uploaded by the system host at any time at the instruction rate. This is because the host interface is dichotomized between internal register and instruction memory.

## 1.1.7. Future Expandability

It should be possible to shrink the chip to denser process geometries. This would improve performance by allowing operation at higher clock rates. Since the chip is designed with a 10-bit Program Counter and 10-bit operand (address) **fields**, we can add GPR, AOR, and instruction memory with minimal layout effort.

# 1.1.8. Internal Operand Busses

The ESP2 contains four 24-bit data busses, W, X, Y, Z. The X and Y busses are time-multiplexed for fetching ALU and MAC unit source operands. These busses connect to the GPR memory array, the AOR memory array, the ALU, the MAC unit, and to all SPRs. The source register (GPR, AOR, or SPR) specified as the ALU's A operand is always fetched on the X buss, as is the MAC unit's D source operand. The register (GPR, AOR, or SPR) specified as the ALU's B source operand is fetched on the Y buss. The register (GPR or SPR, but no AOR) specified as the MAC unit's E source operand is fetched on the Y buss as well. The AOR addressed as the AGEN's G source operand is fetched on the W buss. The Z buss is used to deliver results to the registers (GPR, AOR,

or SPR) designated by destination operands, C and F, from the outputs of the ALU and the MAC unit respectively.

The MAC unit and ALU share the X, Y, and Z busses by relinquishing their use on different phases of the same instruction cycle. Instruction Cycle Timing is covered in the section of the same name.

## 1.1.9. External Interfaces

There are four mechanisms for interfacing to external memory and devices: the external memory interface, the serial interface, the host interface, and chip synchronization.

The **external memory interface** is a 24-bit address, 24-bit data buss for random access of delaylines and tables stored in external memory. This **external memory buss** can also be used to access memory-mapped I/O devices. Addresses for this buss are calculated on every instruction cycle by the AGEN, under program control. The code which drives AGEN can be generated automatically for the programmer by the assembler, if desired. The DIL (Data Input Latch) and DOL (Data Output Latch) SPRs provide the interface to the external memory data buss for incoming and outgoing data as they are accessed as normal sources and destinations of instructions, under program control. The external memory buss cycles at the instruction rate.

The **serial interface** consists of 8 serial stereo data lines. Each of the lines can be configured as input or output. There are two fully programmable sets of clocks for controlling the timing of data transfers on the serial data lines, and each data line can be assigned to either set of clocks. The serial clocks may be disabled to allow exogenous devices to dictate the serial timing. The SER data SPRs (e.g., SER0L) provide the interface to incoming and outgoing serial audio data as they are accessed as normal sources and destinations of instructions, under program control.

The asynchronous **host interface** offers an 8-bit data exchange on the host side, but 24-bit on the ESP2 internal register side. It is described more fully in the later section, Host/ESP2 Interface. The host/ESP2-register interface timing internally parallels that of the ALU; the system host transfers data to/from GPR/AOR/SPR registers using normal ALU data paths (the Y and Z busses). Transfers are <u>completely</u> under ESP2 program control, however, the exact time of the register transfer governed by the ALU HOST and BIOZ instructions. The host will not hang waiting for an acknowledge because built-in semaphores are polled by the host. When the chip is halted, it continually executes HOST instructions by design.

Instruction memory is always accessible to the system host at the instruction rate regardless of the state of the chip. Instruction memory access does not usurp internal chip resources because there is a dedicated 96-bit buss for this purpose (8 bits wide on the host side).

The chip **synchronization interface** includes the IOZ input pin, the IFLAG input pin, the OFLAG output pin, and the RES\ (reset) pin:

The IOZ input pin is most often tied to the system sample rate signal called LRCLK. This signal is asynchronous and comes from <u>any</u> desired source including the ESP2 chip itself. The IOZ pin is indirectly monitored by the ALU BIOZ instruction to synchronize the running ESP2 program to the sample rate.

The IFLAG input pin is uncommitted and can be used for any desired purpose. Its intended purpose is for use as a semaphore in a rapid-transfer DMA scheme. It is visible through the CCR in the ALU as IFLG. Other transfer schemes to external memory are discussed in the Applications section.

The OFLAG output pin is also uncommitted and can be used for any desired purpose. It is connected to the OFLG bit in the HARD\_CONF SPR.

The RES\ pin impact is discussed in the Chip Reset and Initialization section. It can be used in a multi-processor environment to initially synchronize several ESP2 chips running

in parallel. (Provision has been made in the external memory interface for sharing external memory.)  $\,$

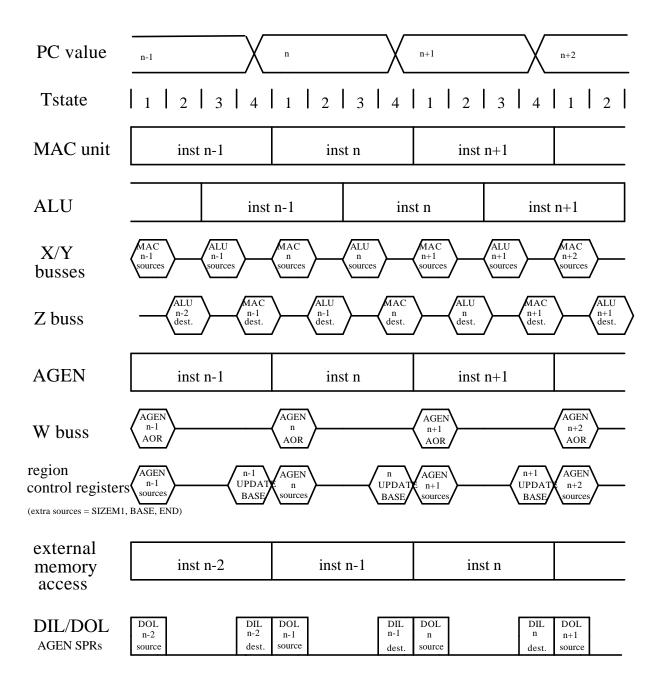

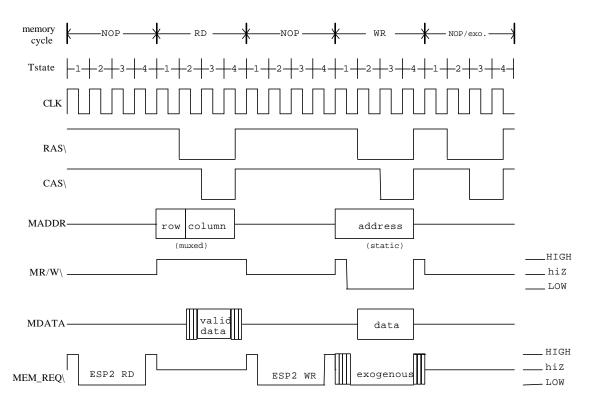

# 1.2. Instruction Cycle Timing

Figure 2. Instruction Cycle Timing diagram

All ESP2 instructions execute in one instruction cycle. The Instruction Cycle Timing diagram shown in Figure 2 illustrates the relative timing of instruction execution for each of the function units (MAC, ALU, AGEN), and their timing relationship with the access to external memory. Notice that the external memory access lags the AGEN instruction requesting it.

The access to internal source/destination operands is also indicated. Execution timing in the MAC unit and ALU are interleaved to allow four operand-fetches and two operandstores by multiplexing the X, Y, and Z busses. By operating these busses at twice the instruction rate, the MAC unit and ALU can each be supplied with two source operands from GPR/AOR/SPRs and have their results stored back into GPR/AOR/SPRs on every instruction cycle.

# 1.3. Latency

There are five categories of execution latency due to the internal pipeline architecture: 1) inter-unit, 2) external memory access, 3) ALU instruction cycle execution, and 4) serial data access, 5) pointer register access for indirect register addressing. The last three categories are discussed in the pertinent sections. With few exceptions, when latencies arise, the latency across the categories is one instruction cycle. This regularity makes for a highly orthogonal design.

# 1.3.1. Inter-Unit Latency

The interleaving of the MAC unit and ALU timing produces some latency in the availability of the result of the ALU instruction with respect to the MAC unit instruction. As illustrated in Figure 2, the MAC unit fetches its source operands for the  $(n+1)^{th}$  queued instruction before the ALU has stored operation results to its destination from the  $n^{th}$  instruction. Similar latencies arise between the AGEN and the ALU since the AGEN fetches are coincident with those of the MAC unit. The AGEN source operands (which include the AOR (address offset), and BASE, SIZEM1, and END region control registers) are acquired at the beginning of an instruction cycle, while there is an optional UPDATE of the region BASE at the end of the cycle.

## 1.3.2. Latency of External Memory Access via AGEN

AGEN must calculate an address during one instruction cycle while the external memory access at that address physically takes place during the next instruction cycle. The external memory data-interface registers, the SPRs called DILs and DOLs, look like any other register to the MAC unit and ALU. In the case of external memory reads (RD), this pipeline design requires the assembler to schedule a RD at least two instruction cycles before the data is actually supplied to the ALU or MAC unit via **DIL** (Data Input Latch). In the case of external memory writes (WR), the pipeline delays the usage of the MAC unit and ALU results written out via **DOL** (Data Output Latch). The pipeline design allows a WR from the MAC unit to external memory to be scheduled as early as the same instruction cycle as the MAC unit instruction which requested it (or any time thereafter). But the pipeline design allows a WR from the ALU to be scheduled no sooner than one instruction cycle after the requesting ALU instruction.

The following manifest quantifies the inter-unit latencies and the AGEN scheduling rules:

The interleaving of the MAC unit and ALU operations and the alignment of the AGEN timing with the MAC unit timing have important ramifications from a programming point of view. The following rules summarize the register data access latencies between function units.

## Nonlatent operations

- 1. The result of a MAC unit operation is available for use as a source operand by the MAC unit no sooner than the next instruction cycle (next queued program line).

- 2. The result of a MAC unit operation is available for use as a source operand by the ALU no sooner than the next instruction cycle.

- 3. The result of an ALU operation is available for use as a source operand by the ALU no sooner than the next instruction cycle.

- 4. The result of a MAC unit operation written to an AOR or AGEN region control register is available to the AGEN no sooner than the next instruction cycle.

#### Latent operations

- 5. The result of an ALU operation is available for use as a source operand by the MAC unit no sooner than the second instruction cycle following the ALU instruction.

- 6. The result of an ALU operation written to an AOR or AGEN region control register is available to the AGEN no sooner than the second instruction cycle following the ALU instruction.

The **scheduling** of DIL/DOL RD/WR from/to external memory, relative to the timing of MAC unit and ALU operand access, follows these rules:

#### Alatent operation

7. External memory writes of MAC unit results to DOL can be scheduled on the same program line (or on any line thereafter) as the instruction which generates the data.

# Nonlatent operation

8. External memory writes of ALU results to DOL can be scheduled no sooner than one instruction cycle after the instruction which generates the data.

#### Latent operation

9. The fetch of data from external memory for use by either the ALU or the MAC unit as a DIL source operand must be scheduled at least two instruction cycles prior to the sourcing instruction.

For a nice programmer's chart, see the ESP2 Language and Software Specification in the Pipeline section.

# 2. Multiplier/Accumulator/Shifter

# 2.1. Architecture

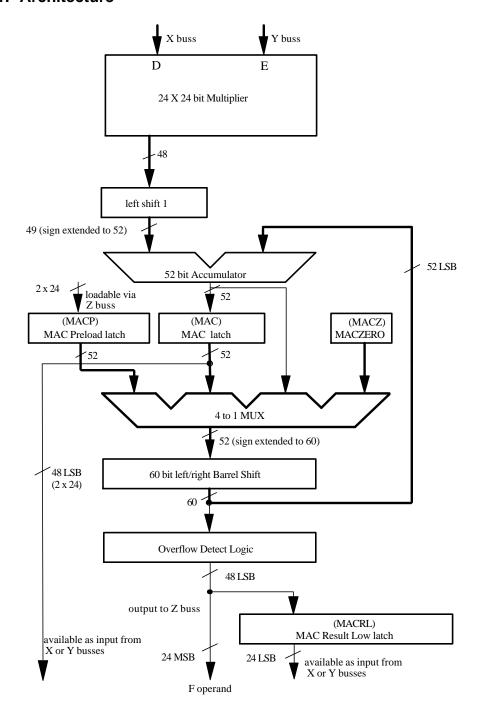

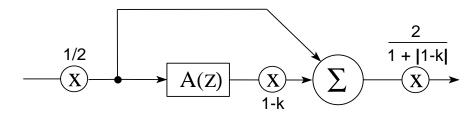

Figure 3. MAC unit architecture. Bold buss shows first half instruction cycle.

The multiplication unit is shown in Figure 3. It consists of a 24 by 24-bit **signed** multiplier, a 52-bit accumulator, a 60-bit left/right arithmetic Barrel Shifter, overflow detect logic, a 4 to 1 MUX and latches. The multiplier sources are fetched on the X and Y buss from registers specified by the D and E operand fields of the instruction. Since the 48-bit product of the 24 by 24-bit fixed-point multiply has two sign bits, a fixed normalizing shift left of 1 bit is designed permanently into the product path. The accumulator adds or subtracts the left-shifted multiplication product, having appended 3 bits of sign extension, to the 52-bit value from the feedback path (bold buss). This allows 4 guard bits for use in detecting overflow in the accumulated result. The accumulator result can then be selectively stored in the MAC latch, or out to a destination, or both. (The symbol labeled 'ACCUMULATOR' has no internal output latch.)

During the first half of an instruction cycle, when the right-side accumulator input is being loaded, the 4 to 1 MUX will select one of three *seed* sources; either the **MAC** latch, the constant MACZERO (**MACZ**), or the MAC Preload latch (**MACP**). These three input options allow:

- 1) accumulation of the multiplier product with the MAC latch,

- 2) multiplication without accumulation,

- 3) accumulation of the multiplier product with a sign-extended (to) 52-bit Preload value (MACP).

Positioning the Barrel Shifter in the feedback path allows shifting of the MAC or MACP latch seeds prior to accumulation.

In the second half of the instruction cycle, there are four destination options:

- 1) 24 MSBs of the double precision accumulator can be written out to a single precision destination register (via the Z buss), and not to the MAC latch,

- 2) to a single precision destination register, and 52-bits to the MAC latch,

- 3) double precision shifted to a single precision destination register, but not shifted to the 52-bit MAC latch,

- **4)** double precision shifted to a single precision destination register, but not shifted and not to the MAC latch.

The accumulator result must propagate through the 4 to 1 MUX, the 60-bit shifter, and the overflow detect logic to the reach the Z buss for writing to a destination register. The shifter and overflow detect logic must be separate so that only the final result of a series of intermediate multiply/accumulate/shift operations becomes conditionally saturated before being written to a destination.

The Barrel Shifter always performs a 60-bit arithmetic shift of 0 to 8 bits left or 0 to 7 bits right. The instruction contains only one shift amount, and the shifter can be used to shift the accumulator right-side input or the accumulator output to a destination register, but not both in the same instruction cycle.

Neither is there any saturation of the left-shifted MAC or MACP latch when used as the accumulator seed input. But when the left-shifted MAC or MACP is used as an accumulator input and then the conditionally saturated result is sent to a destination register, it is possible to detect overflow of these two seed inputs if the overflow is not in excess of 4 bits. This reduction in overflow detection capability for shifts left of the MAC and MACP latch inputs is because of truncation on the feedback path in the MAC unit.

# 2.1.1. Exception Processing

There are two special cases that must be handled by the MAC unit:

# Table 3. Multiplier Exceptions

MAC latch Destination: F,MACRL

\$800000 X \$800000 = \$0,800000,000000 = \$7FFFFF,FFFFFF -\$800000 X \$800000 = \$f,800000,000000 = \$800000,000000

# 2.2. MAC unit Barrel Shifter

The Barrel Shifter residing within the MAC unit performs only arithmetic shifts. The Barrel Shifter performs two functions:

- 1) It can be used on the accumulator output path to perform a shift of +8 (left) to -7 bits of the 52-bit accumulated sign-extended (to 60 bit) result.

- 2) The Barrel Shifter can be applied to the MAC latch as seed-source, or to Preload values in the MACP latch as seed-source, for double precision shifting by +8 to -7 bits.

If it is desired to examine the 4 MAC latch guard bits, this can be done by first right-shifting them in place back into the MAC latch. They can then be examined by sourcing directly from the MAC latch (the SPR MACH).

ASSEMBLER NOTE: The shift code stored in the instruction is an unsigned 4-bit value. The value is derived by the following equation:

Shift code = desired shift amount +7

Since the desired shift amount is in the range from +8 to -7 bits, the result of the Shift code equation falls into the range 0 to 15.

## 2.3. Accessing the MAC unit

The MACP latch is accessible as two pairs of 24-bit write-only SPRs: MACP\_H and MACP\_L, and MACP\_HC and MACP\_LS. *The ESP2 assembler generally disallows any reference to MACP as a source operand which is not the seed source in the MAC unit.* When MACP is used as a single precision destination, this is synonymous with the SPR, MACP\_HC.

The unsaturated MAC latch is directly accessible as a pair of 24-bit read-only SPRs, MACH and MACL, for use as source operands in the ALU or MAC unit with normal latencies. *From the ALU, using the MAC latch as a destination is disallowed by the assembler.* When MAC is used as a single precision source operand, this is synonymous with the SPR, MACH.

# 2.3.1. Writing the MACP (Preload) latch

MACP is used in accumulation, instead of the MAC latch or MACZ, under control of the program. The MACP latch is nonvolatile and will retain a value written to it until written again. Because of the interrelationship between the ALU and MAC unit instruction timing, the value written by the ALU into the high or low-order bits of MACP during the  $n^{th}$  instruction line will be available for accumulation 2 instruction cycles later at the  $(n+2)^{th}$  queued instruction line. The MAC unit can also initialize the high or low-order MACP latch, just as it can load any other SPR. In this case, MACP is available to the MAC unit on the next instruction cycle. The ALU and the MAC unit can be used in conjunction to initialize the full 52 (high and low-order) bits of the MACP latch.

When the SPRs, MACP\_H or MACP\_L, are written, the 24-bit value is written into the indicated half of the MACP latch.

When the SPR, MACP\_HC, is written, 24 bits are written into the high-order half of the MACP latch while the low-order half is cleared to all zeros. When SPR, MACP\_LS, is written, the 24-bit value is written into the low-order half of MACP while the high-order half is written with the sign-extension of the value in the low-order half. These allow MACP initialization to the full 52-bit accumulator width in one instruction cycle.

Any write to the high-order half of the MACP latch is sign-extended into the 4 guard bits to create a full 52-bit word.

# 2.3.2. Reading the MAC latch

Since the MAC latch is located before the overflow detect in the circuit topology, values read from the MAC latch (using the MAC unit SPRs, MACH and MACL, as sources) will <u>not</u> be conditionally saturated. Our intention was to provide unsaturated MAC unit results as source operand for the MAC unit itself as well as for the ALU.

That is to say for many instructions, the MAC unit output is shifted but the MAC latch acting as extra destination is not.

## 2.3.3. MAC Result Low latch (MACRL)

Examination of the fundamental MAC unit instructions shows that the MAC unit has a destination on every instruction cycle. If the programmer does not specify one, the assembler chooses the read-only ZERO SPR as the destination. On every instruction cycle, the low 24 bits of the conditionally saturated MAC unit output will be written to the MAC Result Low latch because it is in the output path. Since MACRL is mapped as an SPR, it is readable by the MAC unit and ALU as a source operand. Storing the low word allows double precision arithmetic using all 48 bits of the final result out of the MAC unit. It is necessary to read the MAC Result Low latch before it is overwritten by the MAC unit in the next instruction cycle. The only exception is when the MAC unit is executing NOPs in which case the contents of MACRL will be preserved (see the MAC unit NOP pseudo instruction).

#### 2.4. MAC unit Instructions

The fundamental instructions executed by the MAC unit are two-source one-destination instructions, having an optional seed source and an optional MAC latch destination, of the form:

When a seed source is not specified, the assembler inserts MACZERO (MACZ). The D and F operands can be any GPR, SPR, or AOR. The E operand can be any GPR or SPR. The F operand acts as the register-type destination. At least one of the two destinations must be specified by the programmer.

When the only destination specified is MAC, the assembler substitutes the read-only SPR called ZERO for the F operand. Unsaturated results of the accumulation are stored in the MAC latch (the SPRs: MACH, MACL) for use in subsequent accumulations.

When the only destination specified is F, the MAC latch is inhibited as a destination. This inhibition is a means to preserve the previous MAC latch contents.

Table 4 lists the fundamental instructions of the MAC function unit: (Parenthesis not required; it only serves to clarify the operation.)

Table 4. MAC unit List of Instructions

```

MACZERO + DXE > MAC >> n > F

MACZERO - DXE > MAC >> n > F

MACZERO + DXE >> n

MACZERO - D X E >>n

> F

MAC + DXE > MAC >> n

> F

MAC - DXE > MAC >> n

> F

(MAC + D X E) >> n

> F

(MAC - D X E) >> n

> F

MAC >> n + D X E

> MAC, F

MAC >> n - D X E

> MAC, F

MAC >> n + DXE

> F

MAC >> n - D X E

> F

MACP + D X E > MAC >> n

> F

MACP - DXE > MAC >> n

> F

(MACP + D X E) >> n

> F

(MACP - D X E) >> n

> F

> MAC, F

MACP >> n + D X E

MACP >> n - D X E

> MAC, F

MACP >> n + D X E

> F

MACP >> n - D X E

> F

```

In six of the instructions in Table 4, notice the MAC latch gets the unshifted unsaturated result while the destination operand, F, gets the shifted and conditionally saturated result. In four other cases, the MAC or MACP latch as seed source is shifted, but the MAC latch as extra destination remains unsaturated. But in all cases, the destination, F, receives the shifted and conditionally saturated result. The shift amount n, as specified

in Table 4, can be +7 to -8 bits; specified as <<n it can be -7 to +8 bits. The shift amount n is a constant expression that is encoded into the micro-instruction word.

# 2.5. MAC unit Pseudo Instructions

The MAC unit pseudo instructions are designed to preserve the MAC latch where possible. Therefore most pseudos do not provide MAC as a destination. Note that the MAC latch is neither a valid destination from the ALU (but MACP is). Generally speaking, only the MAC unit pseudo, NOP, preserves MACRL.

```

ADD D. MAC > MAC. F

= MAC - D X MINUS1 > MAC, F

destination is MAC or F

or both

ADD D, MAC > MAC >> n > F = MAC - D X MINUS1 > MAC >> n > F

ADD D. MAC

= MAC - D X MINUS1 > MAC

ADD D, MAC >> n > MAC

= MAC >> n - D X MINUS1 > MAC

ADD D, MACP > MAC, F

= MACP - D X MINUS1 > MAC, F

! destination is MAC or F

or both

ADD D, MACP > MAC >> n > F

= MACP - D X MINUS1 > MAC >>n > F

ADD D. MACP

= MACP - D X MINUS1 > MACP

ADD D. MACP >> n > MAC

= MACP >>n - D X MINUS1 > MAC

```

The MAC latch as a destination is unsaturated, double precision. MACP as destination is single precision, conditionally saturated.

```

ASH D >>n > F = - D X MINUS1 >>n > F

ASH some_reg >>n = - some_reg X MINUS1 >>n > some_reg

```

This pseudo instruction performs an arithmetic shift n places of the 24 bit D operand. The value n which is encoded in the micro-instruction is the shift range; it is a constant expression which can take any value in the range +7 to -8 bits.

```

ASH D >>8 > F = D X HALF >>7 > F

ASH some_reg >>8 = some_reg X HALF >>7 > some_reg

```

These two extra pseudo instruction definitions make the range of shift for ASH symmetrical. Alternatively the programmer might choose the constant (HALF, MINUS1) to be smaller (using the primitive instruction) thus extending the range of possible shifts right even further.

In a shift right, the programmer should be aware that the MACRL SPR receives all of the bits shifted out of the single precision D operand. This means that bits of the single precision operand are <u>not</u> lost when shifted across the LSB boundary. Considering these pseudo instruction definitions, the 48-bit concatenation, (some\_reg,MACRL), will contain all 24 of the right-shifted bits of some\_reg.

PROGRAMMER NOTE: Double precision SHIFTMAC(P) pseudos or the ALU's double precision shift instructions should also be considered. Note that the ALU's ASH pseudo

instruction can  $\,\underline{not}$  incorporate the MACRL  $\,$  SPR to catch the LSBs as explained here for the MAC unit.

**CLR**

$$F$$

= MACZ + ZERO X ZERO >  $F$

$\label{eq:def_DBL} \textbf{DBL} \ \ D > F \qquad \qquad = \ \ - \ D \ X \ \text{MINUS1} <<1 > F$

**DBL** some\_reg = - some\_reg X MINUS1 <<1 > some\_reg

**EXIT** = MACZ + ZERO X ZERO > REPT\_CNT

This MAC unit pseudo instruction is used to terminate a repeating block of code, instigated by the REPT instruction, <u>at the end</u> of the current block. The MAC unit EXIT pseudo instruction may be placed anywhere within a repeated instruction block **except** for the last line of the block where it will not work at all. See the description of the ALU REPT instruction and the section on SPR Hazards for more details.

**HALVE** D > F =  $-D \times MINUS1 >> 1 > F$

**HALVE** some\_reg = - some\_reg X MINUS1 >>1 > some\_reg

MOV D > F = - D X MINUS1 > F

This allows the multiplier to do a MOV from operand D to operand F. If the D operand is MAC, then the destination will receive the unsaturated MAC latch (MACH) from the previous queued MAC unit operation. This pseudo instruction does not preserve MACRL.

PROGRAMMER NOTE: This instruction uses the MINUS1 SPR (\$800000) as the E operand. MOV to the MAC latch is discouraged because the MACP latch fulfills any role as preload register, and because the MAC latch is not a valid destination from the ALU.

**MOVSMAC** > F = MAC + ZERO X ZERO > F **MOVSMACP** > F = MACP + ZERO X ZERO > F

These pseudo instructions send the double precision conditionally saturated MAC or MACP latch to the single precision destination. If you wish to move the unsaturated MAC latch to a destination, use the MOV pseudo instruction above or the ALU MOV instruction.

**NEG** D > F =  $D \times MINUS1 > F$

**NEG** some\_reg = some\_reg X MINUS1 > some\_reg

# **NOP** = MACRL X ONE >> 1 > ZERO

This NOP for the MAC unit, utilizing the SPR called ONE, preserves MACRL. Since the least significant 24-bits of the MAC unit result are <u>always</u> stored in MACRL, this instruction performs a move of the MACRL SPR to itself. The MAC latch is not written, hence it is preserved. This instruction performs no refresh.

**NORFSH** Identical to NOP

**RFSH** = - REF X MINUS1 > REF

This instruction performs a MOV using the REF SPR as source and destination registers. See the section on GPR and AOR Refresh for details on this SPR and its use in refreshing internal DRAM. Execution of this instruction will cause the loss of the contents of MACRL from the previous queued MAC unit instruction.

**SHIFTMAC** >>n = MAC >>n + ZERO X ZERO > MAC **SHIFTMAC** >>n > MAC = MAC >>n + ZERO X ZERO > MAC **SHIFTMAC** >>n > F = MAC + ZERO X ZERO >>n > F

**SHIFTMACP** >> n > MAC = MACP >> n + ZERO X ZERO > MAC **SHIFTMACP** >> n > F = MACP + ZERO X ZERO >> n > F

The SHIFTMAC and SHIFTMACP pseudo instructions perform an arithmetic shift of the 52 bit MAC latch and MAC Preload latch contents, respectively. The constant expression, n, in the equation is the shift amount; it can take any value in the range -8 to +7 bits. If MAC appears as a destination, it remains unsaturated, but it is shifted with double precision. Unlike the MAC latch, the double precision MACP cannot be shifted in place, which explains why there is no corresponding simplest form of SHIFTMACP. As always, any result written to a destination register (including MACP) is single precision and conditionally saturated.

PROGRAMMER NOTE: The rationale behind the definition of these pseudos is the following:

First, we want double precision results unless a single precision destination register is specified.

Second, consider the construct,

MAC >> n or MACP >> n + ZERO X ZERO > MAC,F

F is conditionally saturated but not guaranteed saturated correctly in a shift left because the MAC unit feedback path is truncated. Therefore, we can only use this construct reliably for SHIFTMAC(P) when the only destination is MAC (F is the ZERO SPR), because the MAC latch is never saturated.

```

SQR some_reg > F = some_reg X some_reg > F

SQR some_reg = some_reg X some_reg > some_reg

```

This is a short hand way of multiplying a number by itself.

ASSEMBLER NOTE: AORs cannot be squared because the MAC unit can only get one source operand from AORs. This event should be flagged as an error for the user.

```

= MAC + D X MINUS1 > MAC, F

SUB D, MAC > MAC, F

destination is MAC or F or

SUB D, MAC > MAC > > F

= MAC + D X MINUS1 > MAC >>n > F

SUB D, MAC

= MAC + D X MINUS1 > MAC

SUB D. MAC >>n > MAC

= MAC >> n + D X MINUS1 > MAC

SUB D, MACP > MAC, F

= MACP + D X MINUS1 > MAC, F

destination is MAC or F

SUB D, MACP > MAC >>n > F = MACP + D X MINUS1 > MAC >>n > F

SUB D, MACP

= MACP + D X MINUS1 > MACP

SUB D. MACP >> n > MAC

= MACP >> n + D X MINUS1 > MAC

```

The MAC latch as a destination is unsaturated, double precision. MACP as destination is single precision, conditionally saturated.

```

XCH some_reg1, some_reg2 = - some_reg1 X MINUS1 > some_reg2 MOV some_reg2 > some_reg1

```

The exchange instruction is a macro-pseudo instruction which uses one MAC unit operation and one ALU operation in order to exchange the contents of two registers. During an XCH instruction, the MAC unit executes a MOV (pseudo) instruction as defined above, while the ALU also executes a MOV instruction but in the opposite direction. Since the operation of the MAC unit and ALU is interleaved, the register contents are swapped using fewer instructions than either function unit acting alone would require.

The complete results are discernible to the ALU on the next instruction cycle, but due to inter-unit latency, only some\_reg2 is discernible to the MAC unit on the instruction cycle following the exchange; there, some\_reg1 still holds its original contents. On the second instruction cycle following the exchange, the complete results are discernible to the MAC unit.

ASSEMBLER NOTE: An XCH specified in the MAC unit instruction field employs both the MAC unit and the ALU, therefore no ALU operation can be specified on that instruction line.

A warning should be issued if indirection is specified because to work properly, the programmer must have set up the INDIRB and/or INDIRC SPRs in the ALU, while it is

| the INDIRD and/or INDIRF ( $\underline{not}$ INDIRE) SPRs which must have been set up in the MAC unit. |

|--------------------------------------------------------------------------------------------------------|

|                                                                                                        |

|                                                                                                        |

|                                                                                                        |

|                                                                                                        |

|                                                                                                        |

#### 3. ALU and Instruction Set

The Arithmetic Logic unit can perform a variety of general and special purpose arithmetic, data movement, and logical operations. It incorporates classical zero-overhead saturation arithmetic for handling computational overflow, and can shift double precision signals to the left or right for the purpose of normalization. Instructions exist to perform unsigned arithmetic without saturation.

During every instruction cycle the ALU takes one or two 24-bit source operands and produces a 24-bit result which is sent to a (third) destination register. ALU execution overlaps with the operation of the MAC unit, so the two computation units operate in parallel. Detailed description of the ALU and MAC unit execution cycles may be found in the section on Instruction Cycle Timing.

The instructions executed by the ALU are three-operand instructions of the form:

#### OPERATION A. B > C

The source A and B operands can be any GPR or SPR or AOR. The C operand is the destination and it can also be any internal register. Since external memory access takes place via the interface SPRs called DIL and DOL, the available operands virtually include external memory data.

Some of the instructions that follow (especially program control instructions) do not use all of the three available operands. Some of the instructions store data in the operand (address) **field**s themselves. Directions have been included showing how the assembler should regard the operands and operand fields of those instructions.

The mnemonic ZERO, used often as an operand, refers to the read-only SPR whose content is zero.

# 3.1. ALU Instructions

These are the fundamental instructions of the ALU:

**ADD** is a saturating 2's complement addition operator used to create the sum of two signals. If the sum cannot be represented in 24 bits, full-scale positive (\$7FFFFF) or full-scale negative (\$800000) is substituted for the overflowed result. The operation performed is:

$$C = A + B$$

**ADDC** Add with carry is a 2's complement saturating addition operator like ADD, but the carry bit in the Condition Code Register (CCR) is added at the LSB. This is valuable for double precision arithmetic. The operation performed is:

$$C = A + B + carry$$

When the ADDC instruction is used in conjunction with a preceding ADDV to perform double precision arithmetic, the ADDC operation can saturate the high 24-bit word of the 48-bit result. Since the low 24-bit word was computed in the preceding ADDV operation, its value will not be conditionally saturated. The low word of the result can be adjusted by the following conditional operation:

```

ADDV a_low, b_low > c_low

ADDC a_high, b_high > c_high

IF OV

{XOR MINUS1, c_high > c_low}

```

(See the section on ALU Pseudo Instructions for the IF pseudo, and see the section on Setting Condition Codes for information on the V flag.)

PROGRAMMER NOTE: Since conditionally executed instructions never modify the Condition Code Register, a double precision addition using the ADDC instruction will <u>not</u> execute properly if the preceding ADDV is conditionally executed {}.

**ADDV** is an unsaturating addition operator. It operates exactly as ADD, except that it lacks overflow detection. For this reason it is not normally used to add signals together, unless the signals are double precision. However, it can be used for generating ramp signals, for performing unsigned address arithmetic, and for double precision arithmetic. It performs the operation:

$$C = A + B$$

**AMDF** This instruction first subtracts the operands as B - A with conditional saturation, and then takes the (one's complement) absolute value of the result.

Equivalent Pseudo-code:

This implementation employing the exclusive OR operation, instead of negation, yields the absolute value of negative numbers which are off by 1, making the magnitude of the destination smaller by one LSB of a 24-bit word in two's complement. This instruction is typically found in pitch detection applications where this error is insignificant. If the error needs to be corrected however, then the state of the N flag in the CCR can be monitored.

**AND** performs the bit-wise logical AND of the two 24-bit operands: C = A & B

**AS** performs an arithmetic shift of B by the contents of A using destination C. Saturation will occur if any of the bits shifted left through the MSB differ from the original sign bit. The shift amount is restricted to the range of +8 to -8 bits. Positive values correspond to left shifts and negative values correspond to right shifts. Zeros enter the LSB during left shifts and the sign enters the MSB during right shifts. (See the ASH pseudo.)

**ASDH** Arithmetic Shift Double High performs a double precision arithmetic shift using the B operand as the high word and the A operand as the low word of a 48-bit input. Saturation will occur if any of the bits shifted left through the MSB differ from the original sign bit. The shift amount for this operation comes from the ALU\_SHIFT SPR and its range is restricted to +8 through -8 bits as in the AS instruction. Zeros enter at the low-word LSB in a left shift, and the sign enters at the high-word MSB in a right shift. The result is the high 24-bit word of the conditionally saturated 48-bit shift output.

ASSEMBLER NOTE: **Switch the operands** on this instruction so that ASDH gpr1,gpr2 gets assembled as gpr2 being the A operand and gpr1 being the B operand. This allows the two halves of a double precision word to appear in proper order. In this particular example, gpr2 is the destination (the C operand).

PROGRAMMER NOTE: See the assembler note above. This switch of the operands hobbles indirection. To indirect on gpr1 the programmer must write to INDIRB, and vice-versa. The programmer must always use the verbose form of the instruction explicitly declaring the destination to successfully implement indirection.

**ASDL** Arithmetic Shift Double Low performs a double precision arithmetic shift using the B operand as the high word and the A operand as the low word of a 48-bit input. The shift amount for this operation comes from the ALU\_SHIFT SPR and its range is restricted to +8 through -8 bits as in the AS instruction. Zeros enter at the low-word LSB in a left shift, and the sign enters at the high-word MSB in a right shift. The result is the low 24-bit word of the 48-bit shift output.

The ALU performs this and the ASDH instruction by intelligently extracting a 32-bit field from the 48-bit input based on shift direction and whether the low or high word is the desired result. When the low word is desired, the MSBs of the input are lost before the shift and are, therefore, not available for detecting overflow during a shift.

ASSEMBLER NOTE: **Switch the operands** on this instruction so that ASDL gpr1,gpr2 gets assembled as gpr2 being the A operand and gpr1 being the B operand. This allows the two halves of a double precision word to appear in proper order. In this particular example, gpr2 is the destination (the C operand).

PROGRAMMER NOTE: See the assembler note above. This switch of the operands hobbles indirection. To indirect on gpr1 the programmer must write to INDIRB, and vice-versa. The programmer must always use the verbose form of the instruction explicitly declaring the destination to successfully implement indirection.

PROGRAMMER NOTE: The result of this instruction will saturate to \$FFFFFF or \$000000 when the V flag in the Condition Code Register is true from the **previous** queued ALU instruction. The direction of overflow will be determined by the N flag of the Condition Code Register from the previous queued ALU instruction.

The N and Z flags will then be set based on the 24-bit result from  $\underline{this}$  instruction, the V flag will not be modified.

If the saturation feature is undesirable, use the LSDL instruction instead.

PROGRAMMER NOTE: Since conditionally executed instructions never modify the Condition Code Register, a double precision shift using the ASDL instruction will not conditionally saturate reliably based on the previous queued ALU instruction if that previous instruction is conditionally executed {}.

**AVG** takes the average of two operands:

$$C = (B + A) >> 1$$

The guard bit of the addition result is included in the shift, therefore overflow is not possible. This means that two full scale signals may be used as inputs without a saturated result. Often used for stereo to monophonic signal conversion.

PROGRAMMER NOTE: The operation, (B - A) >> 1, can be coded using the AVG instruction as follows:

```

AVG somereg_a, somereg_b > somereg_c

SUB somereg_a, somereg_c > some_other_reg

```

This method stores (B+A) >> 1 in somereg\_c. This method also avoids the possibility of saturation in the intermediate result that could occur in the more obvious coding that follows:

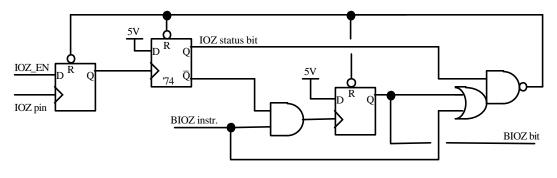

SUB somereg\_a, somereg\_b > somereg\_c AS #-1, somereg\_c > some\_other\_reg **BIOZ** is a sample-rate synchronization instruction which conditionally sets the BIOZ bit in the HOST\_CNTL register. A high BIOZ bit suspends the chip. The BIOZ bit is set when this instruction is encountered and the IOZ status bit of the HOST\_CNTL register is found low. The chip will stay in a state of suspension while the IOZ status bit remains low. Execution will resume when the IOZ status bit is set, for then the BIOZ bit will be automatically cleared. If the IOZ status bit is set before the BIOZ instruction is encountered, then the BIOZ bit cannot go high, hence no suspension will occur. The IOZ status bit is automatically set by a low to high <a href="transition">transition</a> of the IOZ input pin while the IOZ\_EN bit in the HOST\_CNTL register is high. The IOZ pin is an <a href="asynchronous input which is synchronized to the instruction cycle by the synchronization interface.">t is most often tied to the sample rate signal called LRCLK (which is also allowed to be asynchronous with regard to serial data transfer I/O).

Taking the IOZ\_EN bit low will disable the detection of subsequent IOZ input pin transitions, hence disabling the subsequent setting of the IOZ status bit, and will therefore hold the chip in BIOZ suspension <code>indefinitely</code> (assuming that a BIOZ instruction was encountered in the running program). If IOZ\_EN goes low after the IOZ status bit was set, the subsequent BIOZ instruction will observe a high IOZ status bit. Hence, indefinite suspension will occur the next time around. When IOZ\_EN is again set high, the <a href="next">next</a> low to high transition on the IOZ pin sets the IOZ status bit.

All this can be more easily understood by observing the schematic below:

Figure 4

The IOZ status bit appears in the CCR, the HOST\_CNTL interface register, and in HOST\_CNTL\_SPR. The BIOZ instruction automatically monitors the bit which appears in the CCR and which is updated on a per instruction basis. Unlike the IFLAG pin, nowhere does an image of the IOZ input pin exist. The system host has read/write access to the IOZ status bit, the IOZ\_EN bit, and the BIOZ bit through the HOST\_CNTL interface register.

In order to allow run-time host access to internal registers, the ALU will execute HOST instructions but only **while** in suspension; as it does during chip halt (see the section on Halt and Suspension States). The example program and its Equivalent Pseudo-code shows that suspension is not guaranteed by the mere execution of a BIOZ instruction. We see that the instruction cycle corresponding

to the BIOZ instruction itself is used to perform one internal register refresh. Keep in mind that all instructions in the example program are executed only once.

example program: NOP BIOZ NOP  $\begin{array}{ccc} next & queued & instr. \\ 2^{nd} & queued & instr. \end{array}$

# Equivalent Pseudo-code:

```

NOP /* BIOZ bit is always clear

example program: NOP

MOV REF > REF

coming in. */

/* These B and C operands are supplied by the assembler. */

/st Set on low to high transition of IOZ

if (IOZ status bit)

pin. */

clear IOZ status bit

else

set BIOZ bit

execute next queued instr.

/* Execution latency */

if (IOZ status bit) {

clear BIOZ bit

clear IOZ status bit /* Zero it for detection of next sample

period. */

while (BIOZ bit) {

/* Suspension. */

HOST

/* Auto refresh or host access. */

/st B and C operands for HOST are supplied by the hardware as REF. st/

if (IOZ status bit) {

/* Set on low to high transition of IOZ

pin. */

clear BIOZ bit.

clear IOZ status bit

/* Zero for start of next

period. */

}

}

2<sup>nd</sup> queued instr.

execute

```

The BIOZ instruction does not always cause chip suspension. Suspension will <u>not</u> occur when a program main loop equals or exceeds the sample period. BIOZ has an instruction cycle execution latency of 1. If the chip shall enter into a state of suspension then there is a one instruction cycle latency before so. Therefore the instruction line **queued** for execution following BIOZ (which is not necessarily the instruction line at PC value + 1 (See the section on Instruction Cycle Execution Latency.) ) will execute <u>before</u> the suspension becomes effective. When suspension terminates, execution resumes with the  $2^{nd}$  instruction line queued for execution following BIOZ.

PROGRAMMER NOTE: If the number of instruction lines in every program main loop is precisely equal to the sample period, this means that the BIOZ instruction will <u>never</u> allow host access because the chip never goes into suspension. In this case, the programmer must include HOST instructions elsewhere in the code if host access is desired at run-time.

<u>If an occasional program loop exceeds the sample period</u> (which is allowed by the chip synchronization interface), then BIOZ will not allow host access on that particular loop for the same reason.

The BIOZ instruction always performs at least one refresh of internal registers as evidenced by the first line of Pseudo-code. When the application program spends time in suspension (in the while-loop inside the BIOZ instruction) more internal registers are refreshed. The HALT\_REF\_DIS bit in the HARD\_CONF\_SPR must

be low during suspension (or halt) for the HOST instruction in the while-loop to perform refresh when no host access is pending. During halt or suspension, the MAC unit can be forced to do refresh, effectively doubling the refresh rate, if the HALT\_MAC\_REF bit in the HARD\_CONF SPR is set. This doubling comes at the expense of the loss of the contents of the MACRL SPR (the low-order MAC unit result from the queued instruction line executed prior to halt or suspension).

ASSEMBLER NOTE: It is critical that BIOZ be used be perform refresh by setting the B and C operands to the SPR called REF for the MOV operation. The A operand is ZERO.

**BREV** performs a classical bit reverse operation on the full 24 bits of the B operand. This instruction is used in a radix-2 FFT and can be used for FFTs of any binary size up to 2\*\*24. The usage in a loop is the same as for DREV. The operation on the bits is as follows:

```

23 > 0

22 > 1

21 > 2

.

.

.

1 > 22

0 > 23

```

The BREV instruction can also be used to reverse the order of bits emerging or received from the serial interface data lines; e.g.,

```

BREV some_reg > SER2L /* instead of MOV */

```

ASSEMBLER NOTE: The A operand of this instruction is a don't-care. For consistency the ZERO SPR should be used for the A operand.

**DREV** performs a digit reverse operation on the full 24 bits of the B operand. The operation on the bits is as follows:

```

23 > 1

22 > 0

21 > 3

20 > 2

19 > 5

18 > 4

.

.

.

.

.

```

This instruction is used in a radix-4 FFT of any quaternary size up to  $2^{**}24$ . Example of usage in a loop:

```

ADDV \#(2^{**}24)/N, index ! where N = size of FFT DREV index > drev index ! index = 0 -> N-1

```

ASSEMBLER NOTE: The A operand of this instruction is a don't-care. For consistency the ZERO SPR should be used for the A operand.

**HOST** provides host access to GPR/SPR/AOR via the host interface registers. The HOST\_GPR\_PEND bit of the HOST\_GPR\_CNTL interface register is automatically checked by the ESP2 for a host access request. If an access is pending, one MOV instruction is automatically executed which transfers data between the HOST\_GPR\_DATA SPR and internal register memory in the direction specified by the HOST\_GPR\_RW\ bit of the HOST\_GPR\_CNTL interface register. The MOV executes using normal ALU timing and the standard Y and Z busses. The address of the GPR/AOR/SPR to be accessed resides in the HOST\_GPR\_ADDR1,0 interface registers. When the MOV is complete the HOST\_GPR\_PEND bit will automatically clear.

When no host access is pending, this instruction performs refresh of one of the internal GPR/AOR registers.

The BIOZ instruction contains the HOST instruction within it. These two instructions provide the only mechanism for host access to internal registers at run-time. But if the number of instruction lines in every program main loop equals or exceeds the sample period, this means that the BIOZ instruction will <a href="never">never</a> allow host access because the chip never goes into suspension. In that case, the programmer must include HOST instructions elsewhere in the code if host access is desired at run-time.

ASSEMBLER NOTE: If **no** host access is pending, one MOV of B to C automatically occurs in the ALU along the normal data paths using the operands found in the instruction. The B and C operands, then, are both the REF SPR to perform refresh of GPRs/AORs automatically when no host access is pending. (See also the NOP pseudo instruction.)

The A operand of this instruction is a don't-care. For consistency the ZERO SPR is used for operand  $\boldsymbol{A}$ .

**Jcc** Conditional Jump moves the value in the B operand **field** of the instruction into the PC. The A operand **field** of the instruction holds a *condition* mask which controls conditional execution of the instruction by always unconditionally preloading the CMR whenever this instruction is encountered. There is a 1 instruction cycle latency before the PC is modified, therefore the instruction line queued for execution following Jcc is always executed before the jump is made. Conditional execution applies to all instructions. Conditional jumps are performed by conditionally executing the Jcc instruction. If the skip bit is not set for the ALU (i.e., no curly braces in the assembler syntax), the jump is always taken regardless of the preloaded mask. (See the description of the Conditional Execution Mechanism.) *condition* can be GT, GTE, EQ, LT, etc.

ASSEMBLER NOTE: A MOV operation executes along the normal ALU data path. The C operand should be assigned as the ZERO SPR to insure that the MOV is benign. The moves to the CMR and PC use **special** reduced-latency hardware apart from the normal ALU data path. The A operand field of this instruction is set to the ALW Condition Mask if **not** specified.

We strongly discourage the practice of modifying the PC from the ALU using any instruction **not** from the JMP class (Jcc, JScc, RScc) nor REPT, such as MOV. The reason for this is that a sequence of instructions involving MOV to PC and one of the latent instructions, such as BIOZ for example, can have indeterminate outcome. In that example the desired PC value, as vector, varies dependent upon precisely how many instruction cycles the chip remains in suspension.

**JScc** Conditional Jump to Subroutine executes like Jcc, except the value of the PC for the second instruction line **queued** for execution following JScc (which is not necessarily the instruction at PC value + 2 (See the section on Instruction Cycle Execution Latency.) ) is pushed onto a 4-deep hardware stack. The B operand **field** holds the new value of the PC, while the A operand **field** holds a *condition* mask which always unconditionally preloads the CMR whenever this instruction is encountered. Like Jcc, the instruction cycle execution latency of JScc is 1, so the instruction line queued for execution after JScc is always executed before the subroutine is entered.

ASSEMBLER NOTE: A MOV operation executes along the normal ALU data path. The C operand should be assigned as the ZERO SPR to insure that the MOV is benign. The moves to the CMR and PC use **special** reduced-latency hardware apart from the normal ALU data path. The A operand field of this instruction is set to the ALW Condition Mask if **not** specified. Although the PCSTACK0,1,2,3 SPRs are writable by the MAC unit, a hazard will occur if the MAC unit is writing to one of these registers in the same instruction line as a JScc or RScc instruction. It is desirable to detect these events and prevent the programmer from doing this.

PROGRAMMER NOTE. The JScc mnemonic is not recognized by the assembler.

```

Use instead:

```

${JS \ label, \ condition > CMR}$ ! Conditional.

JS *label* ! By default the assembler supplies ALW as the *condition*

Unlike RScc, there is no programmer specified movement from B to the C operand.

# Example of stack management:

CODE /\* push onto PCSTACK \*/

NOP JS here

NOP MOV #some\_PC\_value > PCSTACK0

here: NOP /\* any MAC/ALU/AGEN

instruction \*/

**LIM** is a special operation for checking a ramping value to a upper or lower limit. This instruction is often used for envelope generation. It accepts a limit value as the A operand and a ramping value as the B operand. The instruction also looks at the NA Condition flag to determine the ramp direction. The NA flag in the CCR holds the sign of the A operand from the <u>previous queued</u> ALU operation.

The instruction executes as follows:

```

if (NA == 0) /* If the previous A operand is greater than or equal to zero (POS) ... */ MIN A, B > C else MAX A, B > C

```

This instruction is typically used, for example, in a two instruction block as follows:

```

ADD increment, current_value > current_value LIM limit, current_value > current_value

```

The ADD instruction in this example will set the NA flag with the sign of the increment, which is the direction of the ramp.

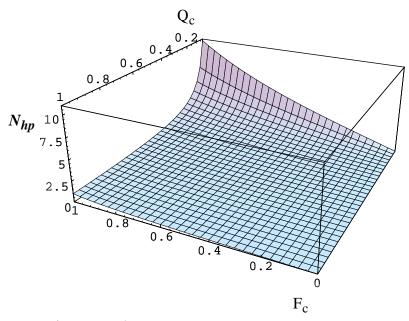

# PROGRAMMER NOTES: